第38回 特許庁とINPITが「タイムスタンプ」を保管するサービスを開始

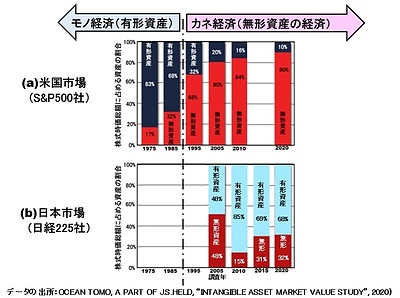

本コラムの第76回及び第77回で指摘したとおり、我が国の科学技術の没落と経済の衰退の進行が激しい。その原因の一つとして、出る杭を打つ気質、即ち、独創研究への投資を嫌い、横並びの同調行動を嗜好する日本人の気質を検討する必要があろう。半導体産業におけるダイナミック・ランダムアクセス・メモリ(DRAM)に参入した我が国の企業の興盛と、その後の衰退の歴史は、競合する相手企業がDRAMで儲けていれば、自社もDRAMの事業をやらないことは許されないという、我が国の経営陣達の無節操な横並び同調気質が寄与した例であろう。

1970年に米国インテル社が最初に1KビットDRAMの商品化に成功すると、1980年代前半までに、次から次へと日本の6~7社以上がDRAM事業へ無節操に参入した。しかし、1990年代の巨額の投資が必要な世代に入ると、独占的競争市場の特質から(以下§3参照。)、DRAM事業に参入してきた外国の他社に利潤を失ってしまい、次々と市場から撤退し全滅している。

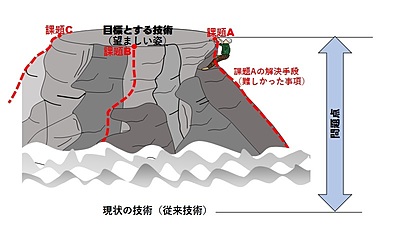

DRAM事業への多数の企業の参入とその後の失敗は、日本人の短期集中型狂乱の気質の発揮であり、独創性に依拠した新規事業を望まない日本人の横並び同調気質による経営に起因しているであろう。独創性があり何処もやっていない事業に基本特許を取得し、基本特許による独占権の保護のもと、過去の実績もない事業に投資するという経営が、我が国の経済を活性化には必要になる。

目次

§1 企業の利潤を最大化する条件

企業の経営陣の注意すべき指標に、投資利益率(ROI)がある。

ROI=(利益金額)/(投資金額)×100(%) ……(1)

である。投資した額に対してどれだけ利益がもたらされたかである。日本企業がDRAM事業から次々に撤退したのは、デザインルールの微細化に伴う巨額の投資金額に見合う利益金額が得られずROIが低下し、赤字化したからである。ROIの低下や赤字化は、日本企業が基本特許を持たない事業に、無節操に次々と参入したことに起因している。

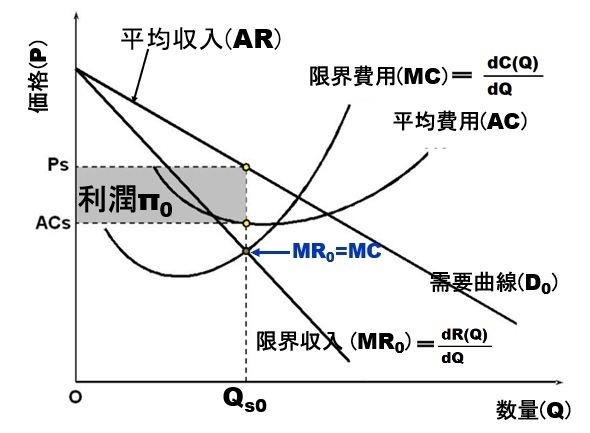

式(1)の右辺の分子である「利益金額」の基礎として、企業の利潤が最大化される条件を、図1を用いて考えてみる。図1の縦軸はDRAM企業が1社で独占している場合におけるDRAMの価格(P)で、横軸はDRAMの数量(Q)である。「独占(供給独占)」とは、DRAM供給者が1社であり財(DRAM)が差別化されている市場のことをいう。「独占市場(供給独占)」においては、財が差別化され市場への新規参入も不可能であり、「独占企業」はDRAMの価格支配力を有する「プライスメイカー」として、自らの利潤を最大化させるように価格を設定することができる。

図1の上側の右下がりの直線はDRAM市場の需要曲線(D_0)である。「独占市場(供給独占)」においては、DRAM市場におけるDRAM供給者が1社しか存在しておらず、すべてのDRAM需要者は唯一の供給者である「独占企業」から供給される財を需要するため、「独占企業」の直面する需要曲線は、市場全体の需要曲線と同じく右下がりの曲線となる。

需要曲線(D_0)の下の傾きの大きな右下がりの直線はDRAM企業の限界収入(MR_0) 曲線である。独占企業の場合は需要曲線(D_0)が平均収入(AR)曲線になり、

(平均収入)×Q=総収入R(Q) ……(2)

であり、限界収入(MR_0)とは、数量Qに依存するDRAM企業の総収入R(Q)を数量Qで微分した値dR(Q)/dQである。限界収入(MR_0)は、DRAMの販売量を1単位(僅かに)変化させたときのDRAM企業の総収入の変化を意味する。

【図1】独占企業の場合の利潤を最大化する条件

図1の中央上側に位置する「下に凸」の曲線は、独占企業がDRAM製造に必要な平均費用(AC)曲線である。平均費用(AC)曲線に交わり、平均費用(AC)曲線の左下に凸部を有するように位置する「下に凸」の曲線は、独占企業がDRAM製造に必要な限界費用(MC)曲線である。

(平均費用)×Q=総費用C(Q) ……(3)

であり、限界費用(MC)は、独占企業のDRAM製造に必要な総費用C(Q)を、DRAMの数量Qで微分した値dC(Q)/dQである。限界費用(MC)は、独占企業がDRAMの生産量を1単位(僅かに)変化させたときのDRAM企業の追加の費用を意味する。独占企業の利潤をπ(Q)とすると、利潤をπ(Q)は、総収入R(Q)から総費用C(Q)を引いた差額であるから、

π(Q)=R(Q)-C(Q) ……(4)

と表現出来る。式(4)の意味するところは、図1では需要曲線(D_0)と平均費用(AC)曲線の差であるから、この差は上に凸の曲線になる。上に凸の曲線の最大値は、式(4)を横軸の数量(Q)での1次微分をゼロにする数量(Q)の場合である。

即ち、式(4)の利潤π(Q)が最大化する条件は、

dπ(Q)/dQ=dR(Q)/dQ-dC(Q) /dQ=MR-MC=0 ……(5)

のとき利潤π(Q)が最大になる。これは、図1に示すように、限界収入(MR_0)曲線と限界費用(MC)曲線が交わるQ=Q_s0となる数量Qにおいて、利潤π(Q)が最大になるということである。

§2 フェアチャイルド社のムーアの予測

次節§3でDRAM市場の特徴を議論する前に、DRAMのメモリセルの高密度化の時間変化を説明する。

インテル社が設立されるおよそ3年前の1965年の4月に、フェアチャイルド社のディレクターであるG.E.ムーア(Moore)が、Electronics誌で、「素子当たりのコストが最小となるように集積回路が数多くの素子を搭載したときに、搭載する素子数は1年に2倍の割合で増加する」と発表した(G. E. Moore, Cramming more components onto integrated circuits”, Electronics, vol.38, no.8, (1965))。

更に、1975年12月の米国電気電子学会(IEEE)のIEDMで、インテル社の創設者であるG.E.ムーアは、微細化とシリコンダイ面積の拡大はこれまでどおりに続くが、1970年代末以降は、集積度の向上ペースが「2年で2倍」に低下するであろうと予測した。この予測が「ムーアの法則」と呼ばれるようになる。

なお、「ムーアの法則」40周年を記念した2005年のインタビューで、「1年で2倍」と「2年で2倍」は自分の発言だが、「18カ月で2倍」と発言したことは一度もないと、G.E.ムーア自信が強く否定している。1K、4K、16K、64K、256K、1M、4M、16Mと、 1970年代~1980年代にDRAMの集積度の拡大ペースが「3年で4倍」であったことが、勝手に「18カ月で2倍」に転じたと思われるが、詳細な理由は不明である。

上記でKは千を意味し「キロ」と読み、Mは百万を意味し「メガ」と読む。例えば16Mは一つの半導体チップの中に、千六百万個のメモリセルが碁盤の目のように、縦横に配列されていることを意味する。

「ムーアの法則」とは、G.E.ムーアの予測に過ぎない。しかも「18カ月で2倍」の方が実際の開発速度に近い傾向で沿っているので、DRAMの実際の開発速度は、厳密には「ムーアの法則」からずれている。

問題は、技術開発者の血の滲むような努力もあったものの、1K、4K、16K、64K、256K、1M、4M、16M、64M、128M、256M、512M、1Gと、いかにも「擬ムーアの法則」に則るかのように、実際にDRAMが開発できてしまった技術的容易性にある。

ここでGは十億を意味し「ギガ」と読む。1Gは一つの半導体チップの中に、十億個のメモリセルが碁盤の目のように配列されていることを意味する。

「擬ムーアの法則」に則ってDRAMが開発できてしまった技術的容易性こそが、DRAM市場への後発企業の参入障壁を低くしている。そして、安易にDRAM市場に参入したDRAM企業が知的財産権による保護を怠ったため、独占的競争市場における競争に負けて、次々と独占的競争市場から撤退した理由になっている。

§3 DRAM市場は、独占的競争市場

「独占的競争市場」とは、財(DRAM)を提供するDRAM供給者が多数存在しているため、競争的ではあるものの、DRAMのビット当たりの単価、チップの厚さやサイズ等、財に対してある程度の構造や性能の差別化がなされている市場のことをいう。独占的競争市場に参入していたDRAM企業は、性能の高いDRAMをいち早く製品化する戦略や,製品化の早さではなくDRAMチップの小型化を重視する戦略で差別化を図っていた。

DRAMの仕様は2000年にDDR SDRAMの標準化がされるまでは、インテル社が決めていたようであるが、その仕様の中で、種々の差別化がされていた。1970年の1KビットDRAMの世代において、日本電気のみがnMOSでDRAMを構成し、先駆のインテル社を含む他社はnMOSより動作速度の遅いpMOSでDRAMを構成しDRAM市場での差別化が存在していた。1973年になると日立がnMOSで4KビットDRAMを構成し、1975年には松下電子がnMOSで4KビットDRAMを構成した商品を開発している。そして1984年になると東芝が、nMOS より消費電力の小さいCMOSで1MビットDRAMの開発に成功し、DRAM市場での差別化がなされていた。

他の独占的競争市場とDRAM市場が異なる特徴は、擬ムーアの法則が示すDRAMの1K、4K、16K、64K、256K、1M、4M、16M、64M、128M、256M、512M、1G、……という流れの高密度化による差別化が必要なことである。これはDRAMのビット当たりの単価の差別化の競争である。独占的競争市場の各企業は、高密度化の開発速度による差別化が必要になるが、開発には世代毎に増大する膨大な投資が必要になる危険を認識する必要があった。

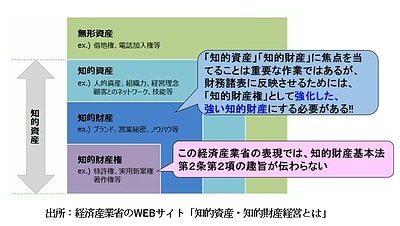

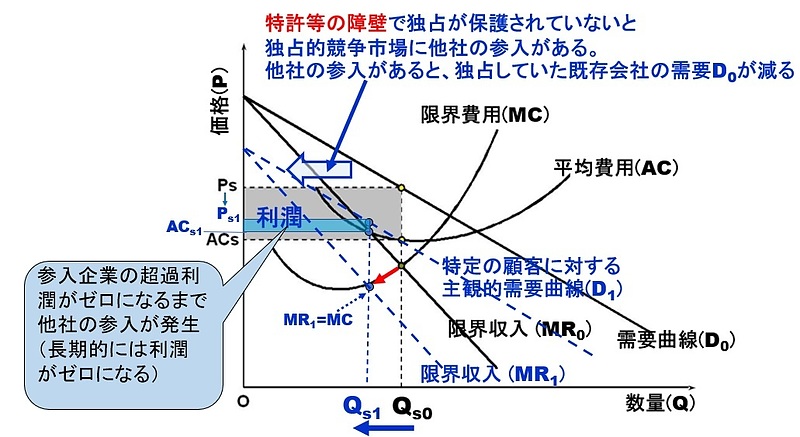

「完全競争市場」は「財(商品やサービス)の供給者が多数存在しており財の特性や形態が同一であること」という条件に基づいた市場である。図1に示した「独占(供給独占)市場」は「DRAM供給者が1社でありDRAMが差別化されていること」という条件に基づいた市場であるが、以下の図2に示す「独占的競争市場」は、完全競争市場と独占市場の中間に位置する市場というイメージになる。

【図2】独占的競争市場の場合の利潤を最大化する条件

図2の縦軸は図1と同様に、独占的競争市場の場合におけるDRAMの価格(P)で、横軸はDRAMの数量(Q)である。図2において実線で示した上側の右下がりの直線は参入企業がない場合の既存会社(先発企業)のDRAM市場の需要曲線(D_0)である。実線の需要曲線(D_0)の下の傾きの大きな右下がりの実線で示した直線はDRAM企業の限界収入(MR_0) 曲線である。

図2において破線で示した上側の右下がりの直線は他社(後発企業)が参入した場合の先発企業のDRAM市場の需要曲線(D_1)である。破線の需要曲線(D_1)の下の傾きの大きな右下がりの破線の直線はDRAM企業の限界収入(MR_1) 曲線である。1984年末に三星社が64KビットDRAMの量産を開始すると、1985年にDRAM市場の急激な価格下落が発生しているように、価格(P)の下落を反映して、破線の需要曲線(D_1)と限界収入(MR_1)曲線は、実線の需要曲線(D_0)と限界収入(MR_0)曲線の下に位置している。

図2の実線で示した中央上側に位置する「下に凸」の曲線は、先発企業がDRAM製造に必要な平均費用(AC)曲線である。平均費用(AC)曲線に交わり、平均費用(AC)曲線の左下に凸部を有するように位置する「下に凸」の実線で示した曲線は、先発企業がDRAM製造に必要な限界費用(MC)曲線である。

式(5)のMR=MCの条件は、図2の独占的競争市場の場合においては、限界収入(MR_1)曲線と限界費用(MC_1)曲線が交わる交点の数量Q=Q_s1で与えられる。即ち、後発企業の参入がある場合には、数量Q=Q_s1の条件において利潤π(Q)が最大になるので、図2から利潤π(Q)を最大にする販売価格P=P _s1である。

同様に、後発企業が参入した場合は、図2から分かるように、利潤π(Q)を最大にする数量Q=Q_s1での製造費用AC=AC_s1であるので、数量Q=Q_s1の最大利潤π_max(Q_s1)は、

π_max(Q_s1)=P _s1-AC_s1 < P _s-AC_s=π_max(Q_s0) ……(6)

となる。図2では、後発企業の参入が無い場合の総利潤を灰色の四角形の面積で示し、独占的競争市場において後発企業が参入した場合の総利潤を、青色の四角形の面積で示している。青色の四角形の方が、灰色の四角形よりも面積が小さくなっている。

図2の独占的競争市場の場合において、参入障壁がなければ、後発企業が参入は超過利潤がゼロになるまで発生し、長期的には独占的競争市場の利潤はゼロになる。

最大利潤π_max(Q_s1)を最大売り上げ総利益(=売り上げー売り上げ原価)とすると、式(1)の右辺分子の「利益金額」の最大値は、

「利益金額」の最大値=π_max(Q_s1)-(投資金額)……(7)

になる。したがって、式(1)の右辺分子は、最大利潤π_max(Q_s1)が小さくなれば、負の値になる場合もある。

DRAM市場を独占的競争市場のモデルで考えれば、後発企業の参入障壁を構築しなければ、長期的な利潤がゼロになる市場である。富士通が汎用DRAM事業から撤退し、日本電気と日立がDRAM事業を統合したエルピーダメモリが発した翌年の2000年1月に、インテル社、マイクロン社、三星社、現代社、インフィニオン社、日本電気の上位5社が、コンソーシアムを設けると発表した。

この発表に先立つ1999年12月の5社の発表では、次世代の1GビットクラスのDRAMでは、他のメモリ会社のコンソーシアムへの参入は認めず、他社がコンソーシアムで開発された技術を利用する際には、ロイヤルティーを徴収すると発表したが、図2に示した独占的競争市場の利潤の減少という性質を考えれば、余りにも遅い判断である。

なお、韓国政府は1999年にLG半導体社と現代社を統合させハイニックス社を成立させている。ハイニックス社は、2012年2月に社名をSKハイニックス社に変更している。インテル社は1985年にDRAM市場を撤退しているが、1980年代に三星社との合弁事業契約を結び、三星社製のチップをインテル・ブランドのもとで販売して三星社を支援していた。更にインテル社は1986年にマイクロン社とDRAM の OEM 供給契約を結び、DRAM市場を裏から支えている。

2001年に東芝は、DRAM部門をマイクロン社に売却してDRAM市場から撤退している。日本電気は1999年に日立のDRAM事業と統合してエルピーダメモリ社を発足させたが、2012年にエルピーダメモリ社が経営破綻すると、2013年にはエルピーダメモリ社がマイクロン社に買収された。1999年にシーメンス社から独立したドイツのインフィニオン社は、DRAM門のキモンダ社を分離独立させ2008年にエルピーダメモリ社と技術提携をしたが、キモンダ社は2009年に経営破綻している。

その結果、2014年以降は、三星社、SKハイニックス社、マイクロン社の3社がDRAM市場のシェアの90%以上を占める独占的競争市場となって安定している。独占的競争市場に多数の企業の安易な参入は、図2に示すように、利潤が減少する必然性があるので、非常に危険である。このことは、参入した多数の半導体企業の淘汰によって歴史が示した。

§4 継続的増大投資が必要な独占的競争市場

横浜中華街、表参道、銀座、秋葉原のような状況が独占的競争市場とされるが、これらの市場は、高密度化の開発速度を競うDRAM市場とは異なり、常に新たな継続的増大投資が必要な市場ではない。

リンゴ生産者全員が同じ製品を売っている完全競争市場の農家は、価格に影響を与えることができない。なぜリンゴにはたくさんの種類があるのかと言えば、農家は自分のリンゴを差別化して成功すれば、競争相手よりも高い価格をつけることができるからである。しかし、リンゴの生産においては、「ムーアの法則」のように常に増大する新たな投資が必要なわけではない。

DRAM市場はビット当たりの単価を安くする競争の市場である。ビット当たりの単価を安くするためには、

(i) ウェハサイズを大きくして、1製造ロットにより製造される各ウェハから切り出されるチップの単価を下げる;

(ii) 1ビットを記録するセルのサイズを小さくして、1チップに集積化されるセルの密度を高くする

の2つの方向がある。完全競争市場における各DRAM製造企業は、この2つの方向で技術革新の速度が求められていた。特に、(i)のウェハサイズを大きくする技術革新には、径の増大したウェハサイズに適するように製造装置全体の入れ替えが必要になる。このため、新たな製造工場の敷地を探し、新たな敷地に建屋を建築する必要が発生し、膨大な投資が求められることになる。

256KビットDRAMまでのセル構造は平面型(プレーナ型)のキャパシタを用いていたが、1MビットDRAMの世代になるとトレンチ型のキャパシタを用いるセルとスタック型のキャパシタを用いるセルが現れたのは(ii)の技術革新である。(ii)のセル構造の技術革新においても、DRAM市場の差別化がなされていた。

トレンチ型のキャパシタは、1975年に日立の角南英夫(1969年西澤研究室卒)が発明し(特許第1264351号)、1980年代後半に、東芝、IBM、シーメンス社、TI社などにより、1MビットDRAMで製品化された。スタック型のキャパシタは1976年に日立の小柳光正(1974年西澤研究室卒)により発明され(特許第1407934号)、1985年に富士通が1Mビットで先行し、4Mビットで日立、三菱、三星社、金星、現代社、マイクロン社、日本電気が採用した。

独占的競争市場となるDRAM市場では更に細かな差別化が試みられ、4MビットDRAMでは大手企業は200~300以上の品種を揃えたという。

日本のDRAM製造企業が1MビットDRAMに移行したとき、三星社が安価な64KビットDRAM や256KビットDRAMを売りさばけたのも、独占的競争市場での差別化である。大手企業が複数世代のDRAMの同時開発体制を構築したのも、独占的競争市場での差別化であるが、複数世代同時開発体制の場合には、それぞれの世代毎の製造装置や製造装置を納める製造工場が必要になる。

又、大型コンピュータに用いる高信頼性の高価なDRAMか、パーソナルコンピュータ(PC)に用いるレベルの信頼性の低価なDRAMかというDRAM市場での差別化がある。

独占的競争市場では参入障壁が低ければ利潤が低化し、DRAMのビット単価を下げるために、世代毎に増大する膨大な投資を競う争いになる危険を、いち早く認識したのは、ムーアの法則のムーアがいるインテル社である。DRAM市場は式(1)の右辺分子の「利益金額」が減少する危険と、式(1)の右辺分母の「投資金額」が増大する危険が、共に世代毎に繰り返される2重帰還が発生する極めて危険な市場なのである。

1985年6月4日にIBMのR.デナードのDRAMの基本特許(USP3,387,286)が存続期間満了すると、基本特許を持たないインテル社は、1985年10月にDRAM市場から撤退した。1985年10月時点では、インテル社は極端に財務が悪化していたわけではないが、MPU事業に戦略転換した。しかも、インテル社は、2023年現在生き残っている三星社とマイクロン社のDRAM事業を裏から支える姑息な戦略を採用し、日本企業はまんまとダマされたのである。

一番抜け目のないのは、基本特許(USP3,387,286)を有していたIBMであった。IBMは独占的競争市場の危険な争いに加わらず、マイクロン社との間にクロスライセンシング協定を締結しマイクロン社を支え、IBM は半球状粒界(HSG) 技術や 化学的機械研磨(CMP) 技術等の多くを供与してマイクロン社の技術発展に大きく関わっていた。IBM 出身のマイクロン従業員がマイクロン社から特許出願もしていたという。

図4に対応するIBMからの日本国特許庁へのDRAMの特許出願の公知件数は、1979年~1982年に各1件、1983年に3件、1986年に1件であった。

§5 クロスライセンシングの多用が日本の経済の衰退を招いた

DRAMの基本特許は、以下に示すように、IBMのR.デナードが1967年に特許出願している(USP3,387,286)。

1926年 J.E.リリエンフェルトがMESFETを発明

(1930年USP1,745,175として登録)

1934年 O.ヘイル(Heil)がMOSFETを発明(英国特許439,457)

1947年 J.バーディーン(Bardeen)とW,H,ブラッテン(Brattain)が

点接触型トランジスタの発見(USP2,524,035)

1948年 W.ショックレー(Shockley)が接合型バイポーラトランジスタを

発明(USP2,569,347)

1950年 西澤が静電誘導型トランジスタ(SIT)を発明(特許第205068号:

特公昭28-60776077の図15がSIT)

1958年 TI社 のJ.キルビー(Kilby)がICを発明(USP3,138,743)

1959年 ベル研のM,M, アタラ(Atalla)とD.カーン(Kahng)がMOSFETを発明、

翌年 アタラが出願(USP3,102,230)

1963年 フェアチャイルド社のR.H.ノーマン(Norman)がSRAMを発明

(USP3,562,721)

1966年 IBMのR.デナード(Dennard)がDRAM考案

1967年 IBMのR.デナードがDRAM特許出願(USP3,387,286)

1967年 ベル研のD.カーン(Kahng)とS.M.シー(Sze)が

浮遊ゲート・不揮発性メモリを発明(USP 3,500,142)

1968年 フェアチャイルド社を退社したムーアがインテル社設立

1968年 日本電気が144ビットのnMOSのSRAMを製品化

1969年 インテル社が64ビットのショットキー・バイポーラSRAMを製品化

1969年 ビジコン(日本計算機販売)の嶋正利がインテル社に

マイクロプロセッサの共同開発を提案(正式契約は1970年)

1969年 インテル社が256ビットのSiゲートpMOSのSRAMを製品化

1970年 インテル社が3トランジスタの1Kビット(=1024ビット)の

pMOSのDRAMを開発製品化

特許権は本来、強力な参入障壁を構成する闘う武器になるはずである。しかし、上記の年表から分かるように、DRAMの基本特許を持たない後発企業である日本の半導体企業は、基本特許に含まれる複数の技術要素の内の特定の技術要素の改良研究をせざるを得ない。したがって、後発企業が特許権を取得したとしても、独占的競争市場において、後発企業の間において、他社と相互にクロスライセンス契約をする横並び同調の戦略で自社の技術を守ることになる。

横並び同調気質に依拠したクロスライセンス契約では、有効な独占的競争市場への参入障壁を構築するのは無理が生じる。その後、独占的競争市場に参入したい更なる後発企業は、クロスライセンス契約に対応可能なように、複数の技術要素に含まれる特定の技術要素に着目して、新たな改良研究をすれば、先に特許権を取得した企業の特許網の中に、孔が開けられるので、独占排他権としての特許権としての性質が失われる。

上述の年表の1950年の西澤潤一先生(第17代東北大総長)が発明した特許第205068号は、SIT以外に、p-i-nダイオード、 p-n-i-pバイポーラトランジスタを含む半導体産業の分野における基本特許である。p-i-nダイオードに関しては米国GE社より僅か18日早かったが、西澤先生が世界で最初の提案者である。半導体産業の黎明期に我が国に半導体企業は、こぞってGE社とライセンス契約をしようとしたが、我が国の外貨審議委員会は、我が国の半導体企業各社とGE社との契約を認めなかった。しかし、我が国の半導体企業のいずれも、西澤先生の特許とのライセンス契約をしなかった。

特許第205068号にp-i-nダイオードと共に記載されたp-n-i-pバイポーラトランジスタは、我が国の高速バイポーラトランジスタの8割が使用していると試算されたが、我が国の半導体企業のいずれもがライセンス契約に応じなかった。

日本の企業とは異なり、p-n-i-pバイポーラトランジスタのライセンス契約に応じるとしたのは、1985年にレーガン大統領に提出したヤングレポートで有名なJ.A.ヤングが当時の社長をしていたヒュレート・パッカード(HP)社のみであった。ヤングレポートの後、米国は特許重視の「プロパテント政策(特許重視政策)」に転じ、日本封じに取りかかる。

我が国の半導体企業のメモリ事業の赤字化が目立ち始めた1997年になって、米国産業界を復活させているのがプロパテント政策であることを、やっと認識する体たらくの事態である。1997 年 4 月に当時の荒井寿光特許庁長官の私設懇談会「21世紀の知的財産権を考える懇談会」で、米国のプロパテント政策による国際競争力の強化が報告された。

そして、東芝がDRAM部門を米国マイクロン社に売却し、DRAM市場から撤退した翌年の2002年2月の小泉首相の施政方針演説を経て、2002年7月に知的財産戦略大綱が発表されたのである。

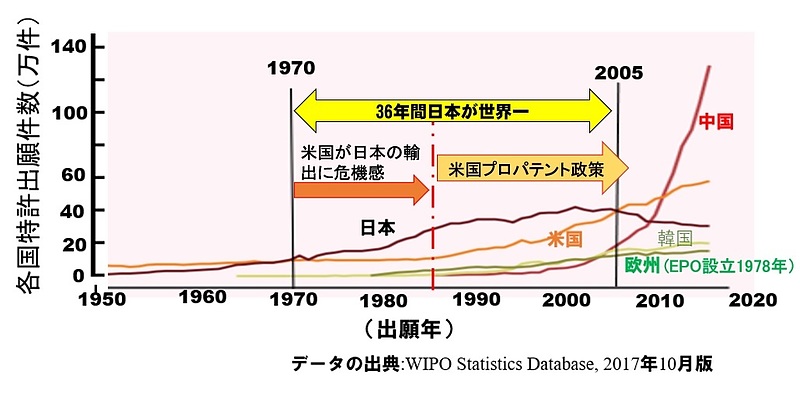

図3に示すように、2002年の知的財産戦略大綱が発表されたときは、我が国の特許出願件数はITバブルの崩壊した年である2001年の43万9千件をピークに、減少の傾向に転じているタイミングである。そして、知的財産戦略大綱の発表の後も、我が国の特許出願件数は減少の傾向にあり、2020年には30万件を下回ってしまい、2001年のピーク値の2/3になろうとしている。図3は減少傾向にあるのは我が国だけであることを、示している。

【図3】レーガン大統領のプロパテント政策以降、急激に米国の特許出願が増える

図3は米国の特許出願件数を示す曲線が1985年に変曲点を有し、急激に増大していることを示し、プロパテント政策の効果が、米国の特許出願件数に現れている。そして、1970年から我が国が2005年まで36年間維持してきた特許出願件数世界一の座を、2006年に米国に譲り渡すことになる(図3をよく見ると、1968年に米国を抜いているので、日本は38年間特許出願件数が世界一であった。)。

p-n-i-pバイポーラトランジスタのライセンス料の事件は、長い間論争がされ、結局、特許第205068号の存続期間が満了してから13年もの後の1983年と1984年に分けて20億円が、西澤先生に支払われることになった。しかし、この20億円は、特許第205068号のライセンス料としてではなく、西澤先生が研究所の所長をされていた(財)半導体研究振興会へ、財団法人への賛助会費の名目で支払われている。

西澤先生のバイポーラトランジスタの事件は、日本の半導体企業がライセンス料を支払うのを嫌い、お互いに相殺して仲良くしたいという横並び同調気質が主因と考える。クロスライセンシングを嗜好する各企業は、クロスライセンシングに適さない西澤先生の基本特許には、特許の正当な評価をしたくなかったのである。

なお、東芝(現キオクシア)が、現在でもなお、フラッシュメモリにおいて一定のシェアを確保している。キオクシアは、舛岡が1980年に発明したNOR型フラッシュメモリ(特許第1421951号)及び1987年に発明したNAND型フラッシュメモリ(特許第2677565号)の2つの基本特許を有している。

キオクシアは経営陣がフラッシュメモリの価値を理解せず、先発会社としての有利性を発揮できなくし、戦略的な大失敗をした。しかし、それでもメモリ分野において、キオクシアが日本の半導体企業のなかの唯一の元気な企業であることは、基本特許の意味を考える上で特筆に値する。

クロスライセンシングにおいて、両者間の特許の量と質に差がある場合には、金銭的な補填が行われる場合もある。しかし、金銭的な補填がされたとしても、特許の相互利用という横並び同調が、クロスライセンシングの前提である(クロスライセンシングの際の補填の事実と、補填金額が公表されることは希であり、補填金額の算定は非常に難しい。)。

クロスライセンシングとは、ライセンス費用の削減のための工夫であり、知財部員は如何にしたら知財費用が低減できるかを考えることが最大の使命となってしまう。しかし、独占的競争市場への後発会社の参入への障壁となる機能を失わせてしまう問題がある。

日本の企業のクロスライセンシング多用の嗜好は、基本特許の独占権としての価値や意味を失わせ、各社が流行を追うことを誘導するものである。そして、クロスライセンシングを多用した結果、独占的競争市場への後発会社の参入を許容し、日本のDRAM事業を全滅させ、日本の経済を低迷させたことに気がつく必要がある。

§6 流行を追うことなかれ

このコラムの第27回で英国キャヴェンディッシュ研究所のW.L.ブラッグ(Bragg)の3原則を紹介した(Freeman J. Dyson, Physics Today, 23(9), pp.23-28, (1970))。3原則の2番目は「流行のテーマを追うな」である。流行を追うのは日本人だけの気質ではないようである。

米国では、プロパテント政策への転換により特許訴訟の提訴数は大きく増加し、1978 年から1999 年の間に約10 倍になったといわれている。1985 年にマイクロン社は日立、富士通、日本電気、三菱、沖電気、東芝の6社に対し、DRAM 市場独占の疑い、シャーマン法、クレイトン法、ウィルソン関税法、1916 年アンチダンピング法の一部違反を理由に提訴している。この提訴が1986年の日米半導体協定締結に繋がったとも言われている。

DRAMのマーケットシェアが次第に低下し業績の悪化した米国TI社は、1986年に我が国の日立、東芝、日本電気、三菱、沖電気、シャープ、富士通、松下の8社と韓国の三星社に対して64KDRAMの輸入差止訴訟を提起した。この輸入差止訴訟は、チップ(前工程)に関する特許ではなく、TI社のA.I.ハイタワー(Hightower)らが1983年に出願したDRAMのパッケージ(後工程)に関するUSP4495376を基礎としている。

この輸入差止訴訟の前に、TI社と日本の8社は、それぞれクロスライセンス契約を結んでいたようである。この輸入差止訴訟でTI社と日本の8社はライセンス料を支払うことで和解し、多額の和解金を得たTI社は、一気に黒字に転じたという。TI社の輸入差止訴訟で被告とされたことから、1986年当時の日本では日立、東芝、日本電気、三菱、沖電気、シャープ、富士通、松下の8社が主にDRAMを製造し、米国に輸出していたことが分かる。

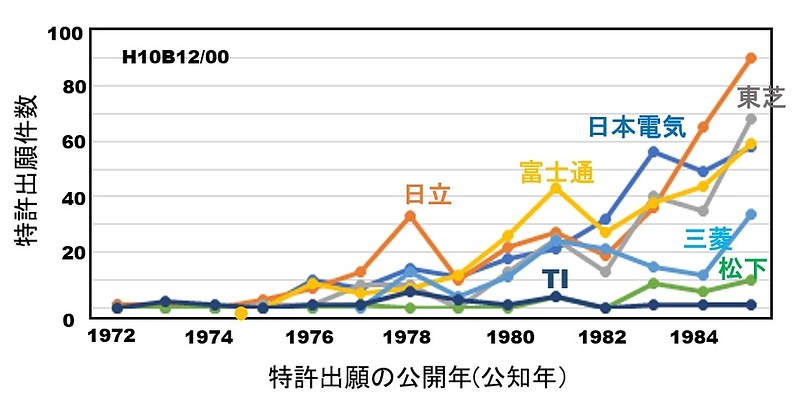

以下の図4はJ-PlatPatのデータを用いて、TI社と日本6社が日本特許庁へDRAMの特許出願したことによる件数の推移を公知年毎に示したものである(輸入差止訴訟の8社から沖電気とシャープを除いている。)。図4のJ-PlatPatの検索ではFI記号H10B12/00を用いた。

【図4】日本6社と米TI社の特許出願の公知年毎の件数推移(日本特許庁)

図4の折れ線グラフのプロット点は公知年で示しているので、実際の出願年は1~2年程度以上遡ることに留意されたい。図4に示された1972年の2件は、日本電気の倉上が特許出願した特願昭46-020707(出願日1971/4/6)と日立の岩松が特許出願した特願昭46-030431(出願日1971/5/10)のデータである。

図4の1973年の2件は、日本電気の若松・岡田の2名が特許出願した特願昭46-074123(出願日1971/9/21)と、日立の増田・増原・永田の3名が特許出願した特願昭46-081692(出願日1971/10/18)のデータである。

日本電気は1981年の売上高世界ランキングの3位であったが、1986年及び1989年の売上高世界ランキングの1位になっている。日立は1981年の売上高世界ランキングの5位であったが、1986年及び1989年の売上高世界ランキングの3位になっている。

TI社の喜田川僖久は、1973年に1トランジスタ+1キャパシタのDRAMの発明を米国特許庁に出願している(USP3940747)が、日本には出願しなかったようである。実は1トランジスタ+1キャパシタのDRAMの発明は、喜田川の特許出願の6年前の1967年に出願されたIBMのR.デナードの基本特許(USP3,387,286)に記載されている。

図4では、TI社は1973年に2件(出願日は1972年)、1974年に1件の日本特許庁への出願が公知になっている。1976年に1件、1976年に1件、1978年に6件、1979年に3件が日本特許庁への出願として公知になっている。TI社は1981年の売上高世界ランキングの1位であったが、1986年及び1989年の売上高世界ランキングの5位に転落している。

日本電気と日立に続き、図4では1975年に東芝の特許出願の1件が公知になり、1976年になると富士通の特許出願が9件公知になっている。東芝は1981年の売上高世界ランキングの6位であったが、1986年及び1989年の売上高世界ランキングの2位になっている。富士通は1981年の売上高世界ランキングの上位10社には含まれていなかったが、1986年に7位、1989年に6位になっている。

1977年に松下の特許出願の1件が公知になっているが、1978~1980年まで松下はゼロで1981年に松下の4件の公知された特許出願がある。松下は1981,1986,1989年の売上高世界ランキングの9位に位置していた(統計の取り方にもよるが、松下は1987年の世界のマーケットシェアの上位10社には含まれていなかった。)。

図4では、1978年には三菱の特許出願が13件公知になっている。三菱は1981年の売上高世界ランキングの上位10社には含まれていなかったが、1986年に10位、1989年に7位になっている。

図4では示されていないが、沖電気の最初の2件の特許出願が公知になるのは1978年である。沖電気は1975年にVLSI開発プロジェクトをスタートし、1978年に16KビットDRAMを出荷している。沖電気の1987年におけるDRAMの世界マーケットシェアは8位であった。

沖電気は1992年、1993年、1994年に台湾のファンドリーであるモセル・バイテリック(Mosel Vitelic)とDRAMの技術供与提携をしている。更に沖電気は1992年に米国キャタリスト・セミコンダクターと、1993年に三星社と、1994年に台湾の南亜塑膠工業(台湾プラスティック)と、それぞれ技術提携をしている。

同様に、図4では示されていないが、シャープの最初の2件の特許出願が公知になるのは1978年である。シャープが福山に半導体第1工場をスタートしたのは1985年である。シャープの1987年におけるDRAMの世界マーケットシェアは10位であった。シャープは1992年にインテル社と技術提携をしている。

図4に示すような多数の企業の参入は、DRAM業界への技術的な参入障壁が低いことを意味しており、特許権等の強固な参入障壁を構築しないと、利潤が減少する危険があることを示すものである。

「産業のコメが鉄から半導体に移った」ということで、1988年から鉄鋼会社の半導体事業への横並び同調の参入が続いた。口火を切ったのは、業界3位の川崎製鉄で1988年に250億円を投じたLSI量産工場を自前で立ち上げた。しかし、2001年に川崎製鉄のLSI事業部を分社化して設立したASICに特化した川崎マイクロエレクトロニクスを、2012年にメガチップスに売却して、半導体事業の市場から撤退している。

これに続き、1993年に業界2位のNKK(日本鋼管)が200億円を投じて半導体事業に参入した。1999年3月にメモリ事業の市場から撤退した。更に、2000年に富士通にASIC/ASSP事業を譲渡して、半導体事業の市場から撤退している。業界1位の新日本製鉄は150億円を投じてDRAM事業に1993年に参入し横並び同調した。新日本製鉄の子会社である日鉄セミコンダクタ(Nippon Steel Semiconductor)は、スイスの銀行UBSが調査したDRAMベンダーランキングで、1995年15位、1996年18位、1997年17位、1998年19位、1999年18位となったが、1999年に日立に売却してDRAM市場から撤退している。

独占的競争市場において参入障壁による制御をせず安易な横並び同調を許すと、図2に示したように利潤が減少し、結局市場から撤退することになることを、歴史が見事に示したことになる。

1986年の輸入差止訴訟で日本の8社と韓国の1社から多額の和解金を得たTI社は、一時経営は改善されたが、1998年にマイクロン社に売却してDRAM市場を撤退している。米国には1980年代半ばまで、8社のDRAM企業があった。1997年にモトローラ社がDRAM市場を撤退して、米国で生き残ったのはマイクロン社の1社だけである。独占的競争市場においては、ライセンス契約による協調ではなく、参入障壁の高さを制御する知財管理が必要ということである。

独占的競争市場の危険性を認識していたのは、ソニーである。ソニーは、図4に示した1982年~1985年の間に2件のDRAMに関する特許出願をしているが、DRAM市場に参入していない。

ソニーは、固体撮像装置の分野で、1975年出願の特許第1215101号、2001年出願の特許第3759435号、2014年出願の特許第5773379号等を基礎に、世界シェアを確保している。特に特許第5773379号に記載された積層型CMOSイメージセンサは、製造には高度なノウハウ技術が必要で、技術的な参入障壁が高いと思われる。

§7 ムーアの法則に縛られることなかれ

そもそも、1966年のIBMのR.デナード(Dennard)が発明したUSP3,387,286や、1973年にTI社の喜田川僖久氏が発明したUSP3940747に記載された1トランジスタ+1キャパシタ方式のDRAMには、原理的に以下の2つの問題点があった。

(a) 1トランジスタ+1キャパシタ方式の問題点の一つは、メモリセルを構成しているキャパシタに蓄電したり、これを開放したりすることで0と1を表現する仕組みであるから、キャパシタへの蓄電/放電の速度には限界がある。キャパシタへの蓄電/放電の速度の問題は、今も改善されていない。

キャパシタへの蓄電/放電の問題に対し、西澤先生は特許第1207716, 1217658, 1225198, 1255126, 1255127号等の蓄積用キャパシタを不要とする構造のSITメモリを提案している。即ち、現在のDRAMで採用されている1トランジスタ+1キャパシタ方式は半導体メモリの最終形態ではない。その他、西澤先生はインテル社が1970年に実現した3トランジスタ型を1トランジスタで実現できる非破壊メモリ(特許第1302745号)や、1素子型SRAM(特許第1399764号)等のSITメモリも提案している。

(b) 2つめは、DRAMへのランダムアクセスの際のアドレスの指定の方法の問題である。マトリクスを構成している行と列にメモリアドレスを分割して与えるという方法を採用したため、DRAMへのランダムアクセスには、どうしても無駄な時間がメモリ・ボトルネックになり、更にワード線やビット線等の配線の寄生容量等や周辺回路による無駄な電力消費を要するようになった。

現状の計算機においては、命令供給とデータ供給の電力消費はクロック/制御ロジックの電力消費と演算の電力消費より比較的大きく、メモリ・ボトルネックによる遅延がある。この理由は、ランダムアクセス方式のメモリとキャッシュとレジスタのすべてがリフレッシュされないことに加えて、これらのキャッシュとレジスタのアクセス方式に起因して大量の配線と一部のソフトウェアのオーバーヘッドによるキャッシュ/レジスタ・アクセスの非効率性に起因すると理解できる。

DRAMは、1K、4K、16K、64K、256K、1M、4M、16M、64M、128M、256M、512M、1Gとひたすらムーアの法則に従うかのように高密度化が進んできた。ムーアの予測は単なる経験則に過ぎないが、いつのまにか、「ムーアの法則」として、独占的競争市場における過酷な開発競争が演じる指針になってしまった。西澤先生は「SITメモリの究極は電子1個のピンポン移動である」と言われていたので、メモリ・ボトルネックが無ければ、デバイ長等の、電子1個を収容するポテンシャル井戸の大きさまでメモリセルの大きさの微細化は可能であろう。

しかし、メモリ・ボトルネックを考慮すると、高密度化はムーアの法則のペースからは崩れる。32ビットのCPUを中心に動くシステムでは、これ以上の高密度化を求めていないので、1G以上にビット数を高めるDRAMの高密度化は、それほど必要がない状況になっている。

1999年の米国半導体工業会(SIA)は、2002年に1Gビット、2003年に2Gビット、2005年に4Gビット、2011年に32Gビットのロードマップを発表したが、現実には2007年にエルピーダメモリから8枚積層した4GビットDRAMの発表があったが、4Gビット以降の開発は進んでいないようである。8枚積層したのでは、チップ内の集積密度を上げたことにはならない。

現在のDRAM企業が取り組んでいるのは、チップに集積されるビット数を高める高密度化ではなく、1個のメモリセルを定義する素子分離(STI)領域のピッチの半分(ハーフピッチ)の寸法を1nmでも小さくして、DRAMチップのサイズを小さくすることである。

計算機のプロセッサの性能にDRAMの速度が追いつけなくなるメモリ・ボトルネックは、DRAMの集積密度が高くなればなるほど、プロセッサの性能の伸びにDRAMの速度が追いつけなくなり、同時に無駄な電力消費が増大して、深刻化する。

スタンフォード大学のW.J.ダリ(Dally)らは、現状の計算機のプロセッサ全体でのエネルギー消費分布を評価した。ダリらは、チップ間の配線を除いた、チップ全体上だけの実際の電力消費分布の評価において、メモリへの命令供給の電力消費は42%、メモリからデータ供給の電力消費は28%、クロックと制御ロジックの電力消費は24%、演算電力消費は6%と評価した(William J. Dally, et al., "Efficient Embedded Computing", Computer, vol. 41, no. 7, 2008, pp. 27-32.)。

そこで、スタンフォード大学のM.J.フリン(Flynn)と中村維男(西澤研究室1972年卒)は、2009年にランダムアクセス方式の使わないで、データの方が隊列を組んで進行するマーチング・メモリを発明した(USP8949650,9361957等)。マーチング・メモリによれば、例えばダリらが評価したメモリからのデータ供給の電力消費を28%から20%に減少させ、メモリへの命令供給の電力消費を42%から30%に減少させ、且つメモリ・ボトルネックを解消することができる。マーチング・メモリにより、演算電力消費電力を6%から10%に、クロックと制御ロジックの電力消費は24%から40%に増大して、高速動作が可能になる。

即ち、マーチング・メモリによれば、メモリへの命令供給の電力消費とメモリからのデータ供給の電力消費の合計を50%にでき、クロックと制御ロジックの電力消費と演算の電力消費の合計を50%にでき、且つ計算機のプロセッサを高速動作させることができることを意味する。

§8 独創研究をして基本特許を取得することが重要

日本の半導体企業のDRAM事業における凋落の背後要因として

(イ)日米半導体協定(1986-1995)による米国の強攻策;

(ロ)1981年のIBMのPCに始まるPC世代における過剰品質;

(ハ)1985年のプラザ合意以降に急速に進んだ円高基調;

(ニ)ファブレスやファンダリモデル等の水平統合型モデルへの対応の後れ;

等の指摘がある。

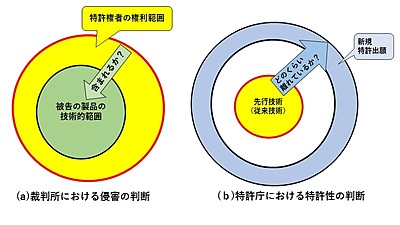

しかし、米国の8社の内で生き残ったのはマイクロン社だけであり、ドイツの企業もDRAM市場から撤退していることを考えると、DRAM市場からの撤退は日本に固有の問題ではない。即ち、上記の(イ)~(ニ)の背後要因よりも、独占的競争市場において、参入障壁が築けず利潤を得ることが出来なかったことが米国やドイツの企業にも共通の要因であろう。そして、米国、ドイツ、韓国および日本等の多数の企業がDRAM市場に参入できたことは、DRAM市場への技術的な参入障壁が低いことを示している。

設備や研究開発(R&D)への投資不足やタイミング遅れや、ものづくり重視・価値づくりや設計軽視の経営スタイルも経営陣側の失敗として、凋落の背後要因になり得る。しかし、経営陣が独占的競争市場の性質や参入障壁の高さの評価を実行できなかったことを、タイミングの遅れや経営スタイルを問題とする前に考えるべきであろう。この点で、ソニーの経営陣は賢明であったと言える。

上述したとおり、日本の半導体企業の凋落の要因は、クロスライセンシングを多用したことにある。クロスライセンシングに依存したのは、強固な独占権を構築できる基本特許が取得できず、改良特許しかなかったことに起因していた、という過去への反省が必要であろう。

1986年TI社が提訴した輸入差止訴訟のとき、当時の日本半導体メーカーは、年間1万件を超える特許を出願し続けていたにもかかわらず、TI社のDRAM特許に1社も対抗できなかった。このとき騒がれたのが「量より質」であるが、強固な独占権を構築できる基本特許でなければ、質が高いとは言えない。

インテル社はDRAM事業から撤退した後、MPU事業においてブラック・ボックス化を図り、MPUの価格の低下を防ぐ戦略を採用した。インテル社のブラック・ボックス化は、図2にモデルを示したような独占的競争市場の特質を理解したからであろう。基本特許が取得出来ず、独占的競争市場への他社の参入を防ぐには、徹底したブラック・ボックス化が必要であり、横並び同調気質を廃する必要がある。

1991年2月に松下電器産業、東芝、三菱、富士通の4社が64MビットDRAMの試作をISSCCで発表しているが、当時は研究者が最先端の研究成果を発表することを競っていた。松下電器産業、東芝、三菱、富士通の4社はDRAM市場から撤退している。徹底したブラック・ボックス化をするのであれば、学会や論文での発表の仕方を工夫すべきである。

このコラムの第15回で述べたように、ブラック・ボックス化した技術の保護は難しい。ブラック・ボックス化した技術は、予めその技術的な外延を明確にしておくことが必要である。

ブラック・ボックス化した技術を保護するためには、秘匿するブラック・ボックス技術とセットになる特許技術を「擬秘匿境界」を示す塀としておき、塀の内部に侵入すれば直ちに侵害したもの検知出来る仕組みが必要になる。したがって、ブラック・ボックス化には、ノウハウとして秘匿する技術と、オープンにしてよい技術との識別が必要になる。

いずれにせよ、今後の日本の経済を活性化するためには、基本特許となりうる独創研究が重要であり、後追い研究をしたのでは国は滅びるのである。

1998年元日の年頭記者会見で、当時の橋本龍太郎首相が西澤先生のp-i-nダイオードの例を出し、日本にも独創研究の開発力があることを述べた(内閣府大臣官房監修、『橋本内閣総理大臣演説集 下』、日本公報協会、p.747、(2001年))。政府は、Rapidusのような外国の技術を導入する会社を支援するのではなく、独創研究を基礎に開発している会社を支援しなければ、DRAMの失敗から何も学習していないことになる。

弁理士鈴木壯兵衞(工学博士 IEEE Life member)でした。

そうべえ国際特許事務所は、「独創とは必然の先見」という創作活動の

ご相談にも積極的にお手伝いします。

http://www.soh-vehe.jp